# 電気学会圧電 MEMS デバイス調査専門委員会 マルチプロジェクトウエハ(MPW)設計ハンドブック

Version 2.0 (H30.3.16 改訂 ver)

作成者: 圧電 MEMS デバイス調査専門委員会 MPW

兵庫県立大学 神田 健介

kanda@eng.u-hyogo.ac.jp

079-267-4870

#### 0. はじめに

本マルチプロジェクトウエハは、圧電薄膜を用いた MEMS デバイス試作の裾野を広げることを目的としております。第1回目は H29 年度 8 月末供給にダイ供給を実施しました。第1回目では試験的に電気学会圧電 MEMS デバイス調査専門委員会の委員を対象として実施しましたが、H30 年度 8 月末供給を予定している第2回 MPW では委員外から広く参加を応募することを予定しています。当プロジェクト自体は営利を目的としたものではないこと、試作費用は海外の商用のものと比較して極めて安価であることについてご配慮いただき、大変心苦しいのですが性能保証は致しかねますことをご承知ください。皆様にご利用いただき、デバイス開発の一助となればと考えております。どうぞ宜しくお願いいたします。

本設計ハンドブックは、デザインルールを含め試作プロセスの設計における注意事項を示したものです。設計データ集約時に試作者が確認を実施いたしますが、労力低減のため、可能な限り本ハンドブックに則り、試作データを設計くださいますようお願いいたします。

なお、試作は調査専門委員会が兵庫県立大学 MEMS デバイス開発支援センターを利用する形で 実施し、設計データ集約完了から 2ヶ月程度でダイを供給することを予定しています。費用につい ては、圧電 MEMS 試作の敷居を下げるという公共の目的のもと、一口あたり試作費用 5 万円(電 気学会会員外 15 万円)および事務処理手数料(経理処理を行なう AffordSENS 社へ)2割、消費税の みを請求いたします。試作依頼方法や契約については、3章の参加方法をご参照ください。

# 1. マルチプロジェクトウエハのプロセスおよびレイヤについて

本章では試作プロセス、および各レイヤについて概要を説明します。設計に際しては、ここで示している各レイヤ名および番号を用いてください。なお、プロセス工程中に示している図中の厚さ比などは分かりやすくするため強調表示しており、サイズ比は不正確であることに注意してください。

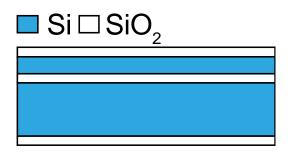

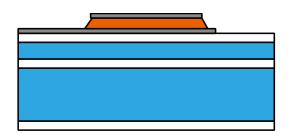

#### (1) 基板および初期酸化工程

SOI ウエハをスターティング基板として使用します。使用する SOI ウエハの仕様は以下の通りです。

- a. \$100 mm (4インチ) ウエハ

- b. 活性層 厚さ:20 μm, N型, 抵抗率 1000-10000 Ω cm

- c. 中間酸化膜 厚さ:1 µm

- d. 支持層 厚さ:500 μm, N型, 抵抗率 15.5 Ω cm

高温下での下部電極形成のため、ウェット熱酸化による酸化膜形成を実施します。1  $\mu m$  厚となるよう形成します。

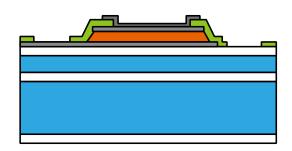

図 1.1 SOI ウエハに熱酸化膜を形成

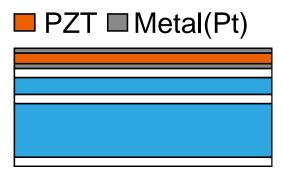

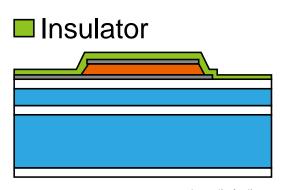

#### (2) 上下電極膜および PZT 薄膜の RF マグネトロンスパッタ法による形成

圧電層には MPB(Zr: Ti = 52: 48)組成の PZT 薄膜を用います。 PZT 薄膜の特性についてはこれまでの経験より、圧電  $d_{31}$  定数は $-40\sim60$  pm/V 程度(抗電界の 50% 未満の低電界駆動時、弾性層が基板厚ではない MEMS カンチレバーに加工後の状態)、ヤング率 82 GPa、誘電率 950 程度、抗電界 50 kV/cm 程度、残留分極 16  $\mu$ C/cm² 程度であることが分かっています(保証値ではありません)。

下部電極である Pt を  $100 \, \text{nm}$  厚、PZT を  $3.0 \, \mu \text{m}$  厚、上部電極である Pt を  $100 \, \text{nm}$  厚で順次 RF マグネトロンスパッタ法により成膜します。Pt 成膜は密着層である Ti を  $10 \, \text{nm}$  厚で成膜した後実施します。

図 1.2 下部電極、PZT、上部電極をスパッタ成膜

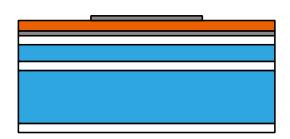

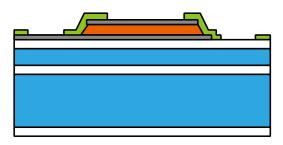

#### (3) <u>上</u>部電極エッチング【マスク No.11 レイヤ名 TE】

上部電極の Pt を ICP-RIE によるドライエッチングによりパターニングします。密着層である Ti も同時にエッチングされます。

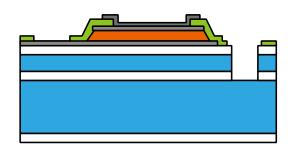

図 1.3 上部電極をドライエッチング

#### (4) PZT エッチング【マスク No.21 レイヤ名 PZT】

PZT 薄膜を ICP-RIE によるドライエッチングによりパターニングします。エッチング 時にはレジストが後退するため、パターンのエッジ部分が 40 度程度のテーパ形状となります。

図 1.4 PZT 薄膜をドライエッチング

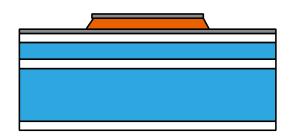

# (5) 下部電極のドライエッチング【マスク No.31 レイヤ名 BE】

下部電極である Pt およびその密着層の Ti を ICP-RIE によりドライエッチングします。

図 1.5 下部電極をドライエッチング

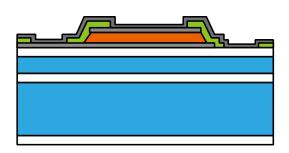

#### (6) 層間絶縁膜の形成

乗り越え配線のための層間絶縁膜である酸化膜を CVD により成膜します。層間絶縁膜にはプラズマエンハンスメント CVD 装置により形成する  $SiO_2$ 膜(Tetraethyl orthosilicate 由来)を用います。 $0.6 \mu m$  厚とします。

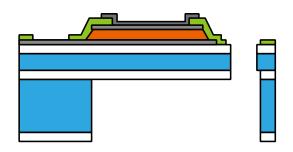

図 1.6 PE-CVD による酸化膜成膜

# (7) 絶縁膜のエッチング【マスク No.41 レイヤ名 INS】

CVDにより形成した酸化膜を ICP-RIE を用いたドライエッチングによりパターニングします。次に成膜する配線電極層によって層間のコンタクトを取るため、層間絶縁膜の必要な箇所にコンタクトホールを配置してください。なお、TEOS-SiO2成膜に伴い、還元雰囲気中の成膜に起因する PZT へのダメージが生じるため、このエッチング後にポストアニール処理を実施します。また、これらの工程において PZT から Pb が SiO2 中へ拡散するため、残留応力によるクラック発生や PZT の組成ずれ等の懸念があります。これらのことに配慮して、PZT 上の領域においては、TEOS-SiO2を残すのは段差乗り越え部のようなショートを防ぎたい部位のみ、最小限になるように設計することを推奨します。

図 1.7 TEOS-SiO<sub>2</sub>膜のドライエッチング

#### (8) 配線電極層のスパッタ成膜

スパッタにより配線電極層である Pt (もしくは Au) を 100 nm 厚で成膜します。

図 1.8 配線層のスパッタ成膜

#### (9) 配線層のドライエッチング【マスク No.51 レイヤ名 WE】

(8) において形成した配線金属層を RIC-RIE を用いたドライ(またはウェット)エッチングによりパターニングします。なお、ボンディングパッドは配線電極層で形成することを推奨します。下部電極や上部電極でボンディングパッドを配置した場合、その後の複数回にわたるドライエッチングにより薄くなり、電極パッドとして機能しなくなるおそれがあります。

図 1.9 配線金属層のドライエッチング

# (10) <u>Si</u>活性層のドライエッチング【マスク No.61 レイヤ名 ACT】

構造体となる Si 活性層を DeepRIE を用いてドライエッチングします。このマスクパターンで表面酸化膜、活性層、中間酸化膜を同時にエッチングします。酸化膜は ICP-RIE によりエッチングします。なお、表面酸化膜単体をエッチングするレイヤが無いため、Si 活性層向けのコンタクトを作製することを想定していません。

また、デザインルールにおいても触れますが、このエッチングは電極や PZT、TEOS-SiO $_2$ 層が全てエッチングされている領域が対象となります。エッチング領域にこれらの層が無いように設計してください。

図 1.10 Si 活性層の DeepRIE によるエッチング

#### (11) Si 支持層のドライエッチング【マスク No.71 レイヤ名 HDL】

Si 支持層を裏面より DeepRIE によりエッチングします。支持層エッチング時に活性層がエッチングされている部位については貫通エッチングとなるため、ダミーウエハへの貼付け後に実施します。この DeepRIE 工程でエッチングされる Si 支持層の断面は逆テーパとなりますので余裕を持った設計とするようお願いいたします。※逆テーパ角はアスペクト比や開口密度に依存しますが、例えば1度逆テーパだとしても500 μm 厚では8.7 μm 程度後退することになります。

図 1.11 Si 支持層の DeepRIE によるエッチング

# 2. デザインルール

#### 2.1 設計における注意事項およびレイヤ情報

設計に際しては、電子回路用の CAD を用いる他、機械設計用の CAD も利用可能です。最終的な提出データはストリームファイル (.str や.gds) 形式のファイルを準備いただくのが最も助かりますが、DXF や IGES 形式も受け入れが可能です。各レイヤの設計データを準備いただき、試作側でデータ確認および統合を行ないます。設計ツールをお持ちでない方でご希望の場合には、兵庫県立大学 MEMS デバイス開発支援センター (http://memskm.dip.jp/MEMSC/) にて設計することも可能です(半日 5000 円。来学いただく必要があります)。その他、受け入れ可能なデータかどうか含め不明な点は個別にご相談ください。

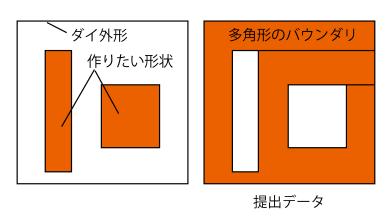

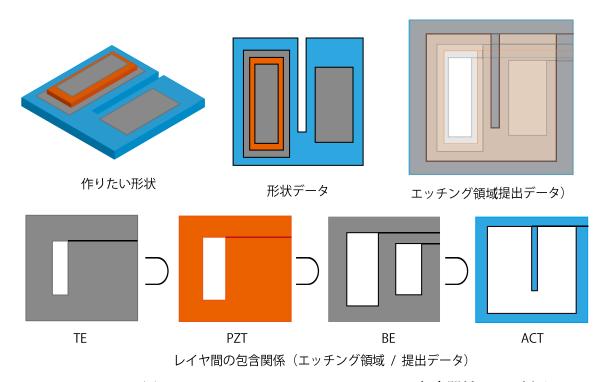

設計するデータにおいて描かれたバウンダリや矩形は、フォトマスクでは光を透過する領域となります。プロセスにおいてはポジレジストを使用するため、提出いただいたデータにおける形状はそれぞれ "エッチングしてなくなる領域"を示すことになります。このエッチング領域について、各プロセスに対応するのがレイヤです。例えば、BEのレイヤにおいて描かれた矩形領域は、下部電極がエッチングされて無くなる領域となります。

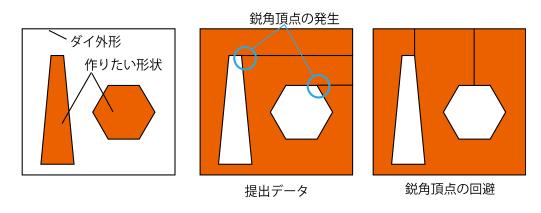

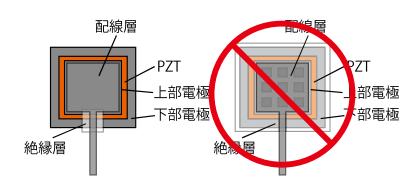

PZT の矩形形状を残す場合には、チップ全体からこの矩形形状をくりぬいたような形状となり、 設計が煩雑となりがちです。そのため、この場合には残すレイヤを設計して、全体から減算するこ とで提出データを作成いただくと良いかと思います(図 2.1 参照)。

本 MPW では、プロセスにおいて対応する全てのレイヤデータをご準備ください。表 2.1 に使用するレイヤ情報をまとめます。提出データにおいては、この表のレイヤ No とレイヤ名を使用するようお願いいたします。

図 2.1 提出データではエッチング領域を多角形のバウンダリとして表示。左図をダイ外形から減 算することで提出データが作成可能

表 2.1 設計レイヤリスト

| レイヤ No | レイヤ名 | レイヤの説明      | 厚み (μm) |

|--------|------|-------------|---------|

| 11     | TE   | 上部電極エッチング   | 0.1     |

| 21     | PZT  | PZT エッチング   | 3.0     |

| 31     | BE   | 下部電極エッチング   | 0.1     |

| 41     | INS  | 絶縁層のエッチング   | 0.6     |

| 51     | WE   | 配線電極エッチング   | 0.1     |

| 61     | ACT  | Si活性層エッチング  | 20      |

| 71     | HDL  | Si 支持層エッチング | 525     |

#### 2.2 デザインルール概要

#### 2.2.1 利用可能サイズ

**ダイ (チップ) サイズ**は **10 mm 角**もしくは **4.8 mm 角**のいずれかになるように設計願います。これらのサイズを超える領域にパターンが無いように設計願います。

#### 2.2.2 鋭角禁止・バウンダリ角数制限

装置の都合上、提出いただくデータにおいて、曲線および鋭角を持つ形状は禁止させていただきます。曲線や斜めの線においてバウンダリが区切られると鋭角となる(図 2.2)のでご注意ください。また、提出データにおいて 90 度以上の角を持つ多角形で形状を設計願います。多角形は 199 角形を限度とします。これらの制約は、複数のバウンダリに分割することや分割する位置を変更することで回避可能です。199 角形以内かつ非鋭角となるようにしてください。曲線については、多角形として設計願います(例えば円であれば正 128 角形にする等)。

図 2.2 設計形状を反転すると生じやすい鋭角頂点。分割位置や角度変更で回避可能

#### 2.2.3 レイヤ内ルール

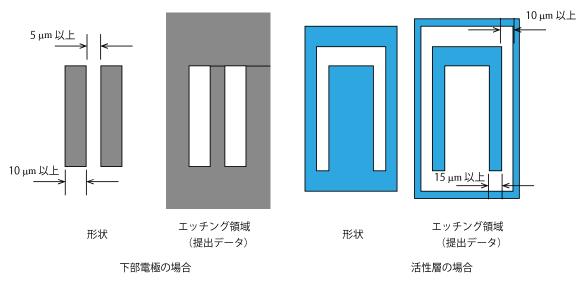

パターンについて、サイズと形状同士の間隔についての制約があります。サイズについての制約の対象は、レイヤによりエッチングされる領域か残る領域か異なります。これらについてのルールを表 2.2 に示します。これらの値は推奨値であり、必ずしも守らなくても良いですが仕上がりに大きな影響を及ぼす可能性があります。

これらの値でも当方の経験上問題ないことは確認できておりますが、PZTの段差乗り越え配線部位については、複数並列配線がショートする、細線が断線するなどの心配もあるので、余裕のあるパターン設計を推奨します。

なお、表中括弧内は強制ルールです。必ず守ってください。具体例を図2.3に記載します。

表 2.2 レイヤ内ルール 対象中:エッチング領域は提出データ、形状はその反転データ (2)は強制ルール

|      |         | (2)(3)(3)(1)(7) |               |

|------|---------|-----------------|---------------|

|      | 対象      | 最小サイズ           | 最小パターン        |

|      | 刈水      | $(\mu m)$       | 間隔(μm)        |

| 上部電極 | 形状      | 10              | 5 (2)         |

| PZT  | 形状      | 10              | 10 <b>(2)</b> |

| 下部電極 | 形状      | 10              | 5 (2)         |

| 絶縁層  | エッチング領域 | 20 <b>(2)</b>   | 5             |

| 配線電極 | 形状      | 10              | 10 <b>(2)</b> |

| 活性層  | エッチング領域 | 15 <b>(2</b> )  | 10            |

| 支持層  | エッチング領域 | 150 <b>(2)</b>  | 50            |

図 2.3 レイヤ内ルールの例

#### 2.2.4 レイヤ間ルール

レイヤ間ルールについては、強制的なルールと任意のルールを設けます。強制的なルールは、遵 守いただかないとプロセスが不可能になるものであり、任意のルールについては、仕上がりに不具 合が生じうるものです。任意のルールについては、必ずしも遵守いただく必要はございませんが、 デバイス仕上がり時に所望の形状が得られないこともございますのでご留意ください。以下の

- (1) および(4) が強制ルールであり、それ以外は任意のルールとなります。なお、数値を含む ルールについては2.3 節に示しますが、強制ルールを太字で示しています。

- (1) 強制ルール 図 1.10の ACT マスクによる DeepRIE の際には、表面酸化膜除去および Si エッチングを行ないます。装置の使用ルールに従うと Si のみがプラズマにさらされる必要があるため、ACT レイヤは BE、PZT、TE、WE の全レイヤ(全てエッチング領域)に包含される必要があります(図 2.4 参照)。

- (2) TE、PZT、BE は積層された状態から順次エッチングされるため、最終形状は必ず TE < PZT < BE のような包含関係となります。また、Si 活性層はこれらの下には必ず存在することになります。よって、TE < PZT < BE < ACT < となります。さらに配線層も必ず Si 活性層上になるため、WE < ACT < となります。図 2.4 参照。

図 2.4 TE,PZT,BE,ACT マスクについての包含関係ルール例示

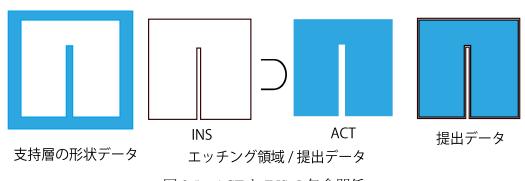

(3) (1) の ACT マスクによる表面酸化膜除去はドライエッチングを想定しています。そのため、CVD 酸化膜が残っている箇所がある場合には酸化膜厚が場所によって異なることになります。これを避けるため、ACT は INS レイヤ(それぞれエッチング領域)を包含するようにしてください(図 2.5)。

図 2.5 ACT と INS の包含関係

- (4) フォトマスクは PG (パターンジェネレータ) により作製いたします。アパーチャ間距離の最小設定値を  $2 \mu m$  としておりますので、これを下回る形状が無いようにお願いいたします。**※強制ルール**

- (5) TEOS-SiO<sub>2</sub> 成膜および後のポストアニール処理では、PZT から SiO<sub>2</sub> への鉛拡散による悪影響がありますので、形状データにおける絶縁層領域は出来る限り小さめにとるようにお願いします (図 2.6)。

絶縁層領域を小さく設計

集積回路では一般的な コンタクトホールタイプ

配線層の段差乗越え配線例(形状データ)

図 2.6 絶縁層領域を小面積で設計

特に PZT 上では絶縁層をあまり残さないようにすることを推奨

- (6) レイヤの異なる形状データ間において、最小の間隔を表 2.3 のように設定します。これは

- (1) ~ (3) の包含関係において包含するほうがはみ出す長さの最小限度に対応します。

例えば、上記(3)のルールに従うと PZT 層は必ず BE 層(ともに形状データ)に含まれていなければならず、この場合の異なる層にある形状のエッジ間の最小距離です。最小  $5~\mu m$  であれば、対象のレイヤにおいて設計した形状のエッジは  $5~\mu m$  以上の距離をとって離す必要があります。すなわち、本ルールが適用されるレイヤ中の形状同士が交わることはありません。

表 2.3 レイヤ間の形状最小間隔ルール(形状データにおいて、左列の各レイヤが上行のレイヤを含む包含関係を示す。距離が記入されている部分がルール適用レイヤ同士となる。)

|      | 上部電極    | PZT     | 下部電極   | 絶縁層    | 配線層     | 活性層 | 支持層 |

|------|---------|---------|--------|--------|---------|-----|-----|

| 上部電極 |         |         |        |        |         |     |     |

| PZT  | ≥ 5 µm  |         |        |        |         |     |     |

| 下部電極 | ≥ 10 µm | ≥ 5 µm  |        |        |         |     |     |

| 絶縁層  |         |         |        |        |         |     |     |

| 配線層  |         |         |        |        |         |     |     |

| 活性層  | ≥ 15 µm | ≥ 10 µm | ≥ 5 µm | ≥ 5 µm | ≥ 10 µm |     |     |

| 支持層  |         |         |        |        |         |     |     |

※太字:包含関係については強制ルール

#### 2.2.5 納品ダイの取り扱いについて

納品時にはダイをダイシングテープで保護した状態で発送します。特に壊れやすい構造の場合には、取り扱いに注意いただき、ダイシングテープからの剥離時にはアセトン等の有機溶剤中に5分程度静置静置してください。液中からの取り出しにも十分ご注意くださいますようお願いします。詳細な取扱注意についての説明書きを同封いたしますので、ご一読の程よろしくお願いいたします。

また、本プロセスにおいては、TEOS-SiO2 成膜後にリカバリアニール処理を行っています。そのため、PZT は脱分極している可能性が高いので、分極処理を行うことを推奨します。分極処理に際しては、下部電極に対して上部電極が負の極性になるよう、ゼロピークで-20Vの交流分極処理(または-20Vの直流分極処理)を10分程度実施してください。

# 3. 参加方法

電気学会圧電 MEMS デバイス調査専門委員会 MPW に参加するには、本ハンドブック最終ページの申込書と設計データを期限までに提出する必要があります。申込・契約  $\Rightarrow$  納品 $\Rightarrow$ 請求となります。請求関係の事務については AffordSens 社( http://www.affordsens.com/ )を介して実施します。

#### 秘密保持および重要事項

- ・試作に際して得られた設計データおよびフォトマスク、試作に際して生じるダミー基板等については調査専門委員会委員長の神田が厳重に保管し、ダイ供給時を起点に2年後に廃棄します。

- ・参加の有無、設計データ、フォトマスク、類推される用途などについて、他の参加者を含め一切、他者への漏洩が無いよう秘密保持を行ないます。

- ・総申込口数については公表いたします。※総申込口数に応じてダイの供給数も変化します。

- ・試作プロセスによって得られた試作ノウハウについては上記の秘密保持契約を遵守した上で公開する場合があります。

- ・また、その他秘密保持についての誓約書または契約が必要な場合には、直接ご連絡ください。

- ・試作・供給されたダイに関しては、商用を含め供給後の扱いには当調査専門委員会および AffordSENS 社は一切関知いたしません。

- ・本プロジェクトにおいて供給するのはベアのチップとなります。ワイヤーボンディングを含む実装等については本プロジェクトとしては実施いたしませんが、兵庫県立大学 MEMS デバイス開発 支援センターにて実施することも可能です。必要であれば別途ご相談ください。

試作データ提出締切:平成30年6月30日(土)23:59

提出方法: Stream、GDS、DXF、IGES 形式の電子データの送付。送付に際しましては、パスワード付き ZIP ファイルを電子メール添付にて提出願います。パスワードは別のメールでご連絡ください。送付後試作者によりデータを確認し修正が必要な場合については個別に対応させていただきます。また、申込書についても押印または署名の上、郵送またはスキャンした pdf を e-mail 添付にて送付ください。

提出先:〒671-2280 姫路市書写 2167 兵庫県立大学姫路工学キャンパス 2 号館 神田 e-mail: kanda@eng.u-hyogo.ac.jp

納品予定日:平成29年9月末日

※供給ダイ数は申込数に依存します。ただし一契約(一口)あたり最小10ダイは保証します。なお、契約数が一口でも提出いただく設計パターンは複数あっても問題ございません。契約一口あたりの提供ダイ数が一定になるようにいたしますので、この場合には複数提出いただいたうちの1設計パターンあたりのダイ提供数が減ることになります。

※なお、申込書中のアンケート中の講習会については希望者が一定数を越えましたら実施させていただきます。また、施設見学は随時可能です。気軽にご連絡ください。

# 改訂履歴

# Ver2.0 H30. 3. 1

第2回 MPW 実施に伴う全面的な改訂

# 電気学会 圧電 MEMS デバイス調査専門委員会 マルチウエハプロジェクト第 2 回試作 申込書

AffordSENS Corporation CEO 樋口行平 様 電気学会圧電 MEMS デバイス調査専門委員会 委員長 神田健介 様

電気学会圧電 MEMS デバイス調査専門委員会 第2回マルチウエハプロジェクトに申込いたします。申し込みに際しては、設計ハンドブックに可能な限り則って設計を行い、データ提出締切日を遵守いたします。また、本ハンドブック3章に示す秘密保持に関する事項に承諾いたします。

所属:

氏名:

#### 申込の方法

必要書類を神田まで以下のいずれかの方法にて送付願います。

- ・スキャン電子メール添付(kanda@eng.u-hyogo.ac.jp)

- ・原本を郵送

(〒671-2280 姫路市書写 2167 兵庫県立大学姫路工学キャンパス 2 号館 神田宛)

#### 試作スケジュールについて

平成 30 年 6 月 30 日(土)23:59 設計申込書・データ提出期限

平成 30 年 9 月 30 日(日) 試作チップ納品予定\*\*

※装置の空き状況、トラブル等不測の事情により早まる場合、遅れる場合があります。

#### 費用について

AffordSENS 社が試作費用の請求をいたします。一口あたり5万円(非会員15万円)に加え事務手数料2割、消費税を試作費用とし、最低10ダイの提供を保障いたします(供給ダイ数はウエハ上のチップ数を申込数で割るので申込数が少なければ増加します)。なお、複数の設計を提出いただくことも可能ですが、その場合にも契約あたりの合計提供ダイ数は変わりません(設計あたりの個数が減ることになります)のでご了承ください。

#### 設計データの提出について

設計データは Stream、GDS、DXF、IGES のいずれかの形式で電子データとしてご提出ください。 可能であればパスワード付き ZIP ファイルを電子メール添付にて提出願います。

> その他不明な点やご希望がございましたら、お気軽に神田までご連絡ください。 兵庫県立大学 神田 健介 kanda@eng.u-hyogo.ac.jp 079-267-4870

#### アンケート

以下の質問にお答えください

MPW の費用は 高すぎる 妥当 安すぎる

MPW の提供するダイのサイズ(10mm,4.8mm 角)は妥当か? YES NO ( mm 角を希望)

MPW の提供するダイの活性層厚さ(20 $\mu$ m)について別の希望がある YES (  $\mu$ m  $\mu$ m  $\mu$ ) NO

本試作プロセスに関する講習会の実施について 実施するならば参加したい 参加を希望しない